Unveil The Power Of Verilog's "else If": Enhance Your Coding Skills

Christopher Snyder

Christopher Snyder

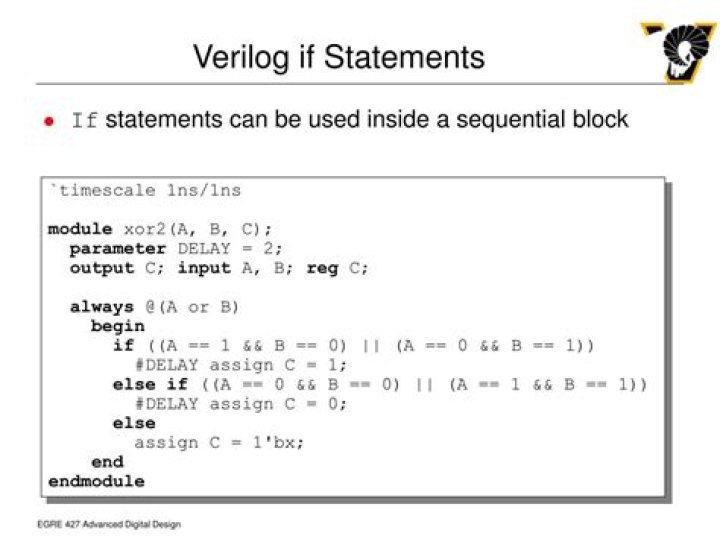

In the Verilog programming language, the "else if" statement is a conditional statement that allows for multiple conditions to be evaluated in sequence. It is used to execute a specific block of code only if a specified condition is true, otherwise it will move to the next condition. The syntax of the "else if" statement is as follows:

if (condition1) begin // code to be executed if condition1 is trueend else if (condition2) begin // code to be executed if condition2 is trueend else begin // code to be executed if neither condition1 nor condition2 is trueend

The "else if" statement can be used to create complex decision-making logic in Verilog code. It is a powerful tool that can be used to implement a wide variety of algorithms and applications.

Here are some of the benefits of using the "else if" statement:

- It allows for multiple conditions to be evaluated in sequence.

- It can be used to implement complex decision-making logic.

- It is a powerful tool that can be used to implement a wide variety of algorithms and applications.

The "else if" statement is an important part of the Verilog programming language. It is a versatile tool that can be used to create a wide variety of logic circuits.

verilog else if

The "verilog else if" statement is a powerful tool that can be used to implement complex decision-making logic in Verilog code. It is a versatile tool that can be used to create a wide variety of logic circuits.

- Conditional statement: The "else if" statement is a conditional statement that allows for multiple conditions to be evaluated in sequence.

- Multiple conditions: It can be used to evaluate multiple conditions in sequence, and execute different code blocks based on the evaluation results.

- Complex logic: It can be used to implement complex decision-making logic, such as nested if-else statements or switch-case statements.

- Code readability: It improves code readability by organizing conditional statements in a clear and structured manner.

- Versatile: It is a versatile tool that can be used to implement a wide variety of algorithms and applications.

- Nested statements: It can be used to create nested if-else statements, allowing for more complex decision-making logic.

- Default case: It can be used together with an "else" statement to provide a default case when none of the conditions are met.

- Alternative to switch-case: It can be used as an alternative to switch-case statements, providing a more flexible way to handle multiple conditions.

The "else if" statement is an important part of the Verilog programming language. It is a powerful tool that can be used to create a wide variety of logic circuits. By understanding the key aspects of the "else if" statement, you can use it effectively to implement complex decision-making logic in your Verilog code.

Conditional statement

The "else if" statement is a powerful tool that can be used to implement complex decision-making logic in Verilog code. It is a conditional statement that allows for multiple conditions to be evaluated in sequence. This means that you can check for multiple conditions, and execute different code blocks based on the evaluation results.

- Facet 1: Conditional evaluation

The "else if" statement allows you to evaluate multiple conditions in sequence. This means that you can check for multiple conditions, and execute different code blocks based on the evaluation results. For example, you could use an "else if" statement to check for different values of a variable, and execute different code blocks depending on the value of the variable.

- Facet 2: Code organization

The "else if" statement can be used to organize your code in a clear and structured manner. By using "else if" statements, you can avoid using nested if-else statements, which can make your code more difficult to read and understand.

- Facet 3: Complex decision-making

The "else if" statement can be used to implement complex decision-making logic. For example, you could use an "else if" statement to check for multiple conditions, and execute different code blocks based on the evaluation results. This can be useful for implementing algorithms or applications that require complex decision-making logic.

- Facet 4: Versatility

The "else if" statement is a versatile tool that can be used to implement a wide variety of algorithms and applications. It is a powerful tool that can be used to create complex decision-making logic in Verilog code.

In conclusion, the "else if" statement is a powerful tool that can be used to implement complex decision-making logic in Verilog code. It is a conditional statement that allows for multiple conditions to be evaluated in sequence. This makes it a versatile tool that can be used to implement a wide variety of algorithms and applications.

Multiple conditions

The "else if" statement in Verilog is a powerful tool that allows for multiple conditions to be evaluated in sequence. This means that you can check for multiple conditions, and execute different code blocks based on the evaluation results. This is a very useful feature that can be used to implement complex decision-making logic.

- Facet 1: Conditional branching

The "else if" statement allows you to evaluate multiple conditions in sequence. This means that you can check for multiple conditions, and execute different code blocks based on the evaluation results. For example, you could use an "else if" statement to check for different values of a variable, and execute different code blocks depending on the value of the variable.

- Facet 2: Nested conditions

The "else if" statement can be used to create nested conditions. This means that you can check for multiple conditions, and execute different code blocks based on the evaluation results of the nested conditions. For example, you could use an "else if" statement to check for different values of a variable, and then use another "else if" statement to check for different values of another variable.

- Facet 3: Complex decision-making

The "else if" statement can be used to implement complex decision-making logic. For example, you could use an "else if" statement to check for multiple conditions, and execute different code blocks based on the evaluation results of the conditions. This can be useful for implementing algorithms or applications that require complex decision-making logic.

In conclusion, the "else if" statement in Verilog is a powerful tool that allows for multiple conditions to be evaluated in sequence. This makes it a versatile tool that can be used to implement complex decision-making logic.

Complex logic

The "else if" statement in Verilog is a powerful tool that can be used to implement complex decision-making logic. This is because it allows for multiple conditions to be evaluated in sequence, and different code blocks to be executed based on the evaluation results.

One common use of the "else if" statement is to implement nested if-else statements. This can be useful when you need to check for multiple conditions, and execute different code blocks depending on the results of the conditions. For example, you could use nested if-else statements to check for different values of a variable, and execute different code blocks depending on the value of the variable.

Another common use of the "else if" statement is to implement switch-case statements. This can be useful when you need to check for multiple values of a variable, and execute different code blocks depending on the value of the variable. For example, you could use a switch-case statement to check for different values of a variable, and execute different code blocks depending on the value of the variable.

The "else if" statement is a versatile tool that can be used to implement a wide variety of complex decision-making logic. It is a powerful tool that can be used to create complex logic circuits.

Code readability

The "else if" statement in Verilog is a powerful tool that can be used to improve code readability by organizing conditional statements in a clear and structured manner. This is because it allows for multiple conditions to be evaluated in sequence, and different code blocks to be executed based on the evaluation results.

- Facet 1: Conditional branching

The "else if" statement allows you to evaluate multiple conditions in sequence. This means that you can check for multiple conditions, and execute different code blocks based on the evaluation results. This can help to improve code readability by making it clear which code blocks will be executed under which conditions.

- Facet 2: Nested conditions

The "else if" statement can be used to create nested conditions. This means that you can check for multiple conditions, and execute different code blocks based on the evaluation results of the nested conditions. This can help to improve code readability by making it clear which code blocks will be executed under which conditions.

- Facet 3: Code organization

The "else if" statement can be used to organize code in a clear and structured manner. This is because it allows you to group related code blocks together, and to separate them from unrelated code blocks. This can help to improve code readability by making it easier to understand the flow of the code.

- Facet 4: Reduced complexity

The "else if" statement can help to reduce the complexity of code by eliminating the need for multiple if-else statements. This can help to improve code readability by making it easier to understand the flow of the code.

In conclusion, the "else if" statement in Verilog is a powerful tool that can be used to improve code readability by organizing conditional statements in a clear and structured manner. This can make it easier to understand the flow of the code, and to identify and fix errors.

Versatile

The "else if" statement in Verilog is a versatile tool that can be used to implement a wide variety of algorithms and applications. This is because it allows for multiple conditions to be evaluated in sequence, and different code blocks to be executed based on the evaluation results.

- Facet 1: Implementing complex algorithms

The "else if" statement can be used to implement complex algorithms by breaking them down into a series of smaller steps. Each step can be implemented as a separate code block, and the "else if" statement can be used to control the flow of execution between the steps.

- Facet 2: Creating reusable components

The "else if" statement can be used to create reusable components that can be used in multiple algorithms and applications. For example, you could create a component that implements a specific mathematical function, and then use the "else if" statement to instantiate the component in different parts of your code.

- Facet 3: Implementing state machines

The "else if" statement can be used to implement state machines by defining a set of states and transitions between the states. The "else if" statement can be used to control the flow of execution between the states, and to execute different code blocks depending on the current state.

- Facet 4: Implementing test benches

The "else if" statement can be used to implement test benches by defining a set of test cases. The "else if" statement can be used to control the flow of execution between the test cases, and to execute different code blocks depending on the results of the test cases.

In conclusion, the "else if" statement in Verilog is a versatile tool that can be used to implement a wide variety of algorithms and applications. It is a powerful tool that can be used to create complex logic circuits.

Nested statements

The "else if" statement in Verilog is a powerful tool that can be used to create nested if-else statements, allowing for more complex decision-making logic. This is because the "else if" statement allows for multiple conditions to be evaluated in sequence, and different code blocks to be executed based on the evaluation results.

For example, the following code uses nested "else if" statements to check for different values of a variable, and execute different code blocks depending on the value of the variable:

if (variable == 1) begin // Code block 1 end else if (variable == 2) begin // Code block 2 end else if (variable == 3) begin // Code block 3 end else begin // Code block 4 end

This code checks for three different values of the variable, and executes a different code block for each value. This is a powerful feature that can be used to implement complex decision-making logic.

Nested "else if" statements can be used to implement a wide variety of complex decision-making logic. For example, they can be used to implement state machines, finite state machines, and decision trees.

In conclusion, the "else if" statement in Verilog is a powerful tool that can be used to create nested if-else statements, allowing for more complex decision-making logic. This is a versatile tool that can be used to implement a wide variety of algorithms and applications.

Default case

The "else" statement in Verilog is used to provide a default case when none of the conditions in the "else if" statements are met. This is useful for ensuring that there is always a code block that is executed, regardless of the values of the conditions.

For example, the following code uses an "else" statement to provide a default case for a variable:

if (variable == 1) begin // Code block 1 end else if (variable == 2) begin // Code block 2 end else begin // Default code block end

In this example, if the variable is equal to 1, then code block 1 will be executed. If the variable is equal to 2, then code block 2 will be executed. If the variable is not equal to 1 or 2, then the default code block will be executed.

The "else" statement is a powerful tool that can be used to ensure that there is always a code block that is executed, regardless of the values of the conditions. This is useful for preventing errors and ensuring that the code always behaves as expected.

Here are some of the benefits of using the "else" statement:

- It ensures that there is always a code block that is executed, regardless of the values of the conditions.

- It prevents errors and ensures that the code always behaves as expected.

- It is a versatile tool that can be used in a variety of situations.

In conclusion, the "else" statement is a powerful tool that can be used to improve the quality and reliability of Verilog code.

Alternative to switch-case

The "else if" statement in Verilog is a powerful tool that can be used as an alternative to switch-case statements. This is because it allows for multiple conditions to be evaluated in sequence, and different code blocks to be executed based on the evaluation results.

One of the main advantages of using the "else if" statement over the switch-case statement is that it is more flexible. The switch-case statement requires that the conditions be constants, while the "else if" statement allows the conditions to be any expression. This makes the "else if" statement more versatile and easier to use in a wider variety of situations.

For example, the following code uses a switch-case statement to check for different values of a variable:

switch (variable) { case 1: // Code block 1 break; case 2: // Code block 2 break; case 3: // Code block 3 break; default: // Default code block break; } The following code uses an "else if" statement to check for different values of a variable:

if (variable == 1) begin // Code block 1 end else if (variable == 2) begin // Code block 2 end else if (variable == 3) begin // Code block 3 end else begin // Default code block end

As you can see, the "else if" statement is more flexible than the switch-case statement because it allows the conditions to be any expression. This makes the "else if" statement a more powerful tool for handling multiple conditions.

In conclusion, the "else if" statement in Verilog is a powerful tool that can be used as an alternative to switch-case statements. It is more flexible and easier to use in a wider variety of situations.

Frequently Asked Questions about "verilog else if"

This section addresses common questions and misconceptions about the "verilog else if" statement.

Question 1: What is the purpose of the "else if" statement?

Answer: The "else if" statement is a conditional statement that allows for multiple conditions to be evaluated in sequence. It is used to execute different code blocks based on the evaluation results of the conditions.

Question 2: How is the "else if" statement different from the "if" statement?

Answer: The "else if" statement is similar to the "if" statement, but it allows for multiple conditions to be evaluated in sequence. The "if" statement only allows for one condition to be evaluated.

Question 3: When should I use the "else if" statement?

Answer: The "else if" statement should be used when you need to evaluate multiple conditions in sequence and execute different code blocks based on the evaluation results of the conditions.

Question 4: What is the syntax of the "else if" statement?

Answer: The syntax of the "else if" statement is as follows:

if (condition1) begin // code to be executed if condition1 is trueend else if (condition2) begin // code to be executed if condition2 is trueend else begin // code to be executed if neither condition1 nor condition2 is trueend

Question 5: Can I nest "else if" statements?

Answer: Yes, you can nest "else if" statements. This allows you to create complex decision-making logic.

Question 6: What is the difference between the "else if" statement and the "switch" statement?

Answer: The "else if" statement is more flexible than the "switch" statement because it allows the conditions to be any expression. The "switch" statement requires that the conditions be constants.

Summary: The "else if" statement is a powerful tool that can be used to implement complex decision-making logic in Verilog code. It is a versatile tool that can be used in a variety of situations.

Transition to the next article section: This concludes the FAQs about the "verilog else if" statement. In the next section, we will discuss the benefits of using the "else if" statement.

Tips for Using the "verilog else if" Statement

The "else if" statement is a powerful tool that can be used to implement complex decision-making logic in Verilog code. Here are some tips for using the "else if" statement effectively:

Tip 1: Use the "else if" statement to evaluate multiple conditions in sequence.

The "else if" statement allows you to evaluate multiple conditions in sequence and execute different code blocks based on the evaluation results. This can be useful for implementing complex decision-making logic.

Tip 2: Use the "else if" statement to create nested decision-making logic.

The "else if" statement can be used to create nested decision-making logic. This can be useful for implementing complex decision-making logic.

Tip 3: Use the "else if" statement to provide a default case.

The "else if" statement can be used to provide a default case. This can be useful for ensuring that there is always a code block that is executed, regardless of the values of the conditions.

Tip 4: Use the "else if" statement as an alternative to the "switch" statement.

The "else if" statement can be used as an alternative to the "switch" statement. This can be useful for implementing complex decision-making logic.

Tip 5: Use the "else if" statement to improve the readability of your code.

The "else if" statement can be used to improve the readability of your code by organizing conditional statements in a clear and structured manner.

By following these tips, you can use the "else if" statement effectively to implement complex decision-making logic in your Verilog code.

Summary: The "else if" statement is a powerful tool that can be used to implement complex decision-making logic in Verilog code. By following the tips outlined in this article, you can use the "else if" statement effectively to improve the quality and readability of your code.

Conclusion

The "else if" statement is a powerful tool that can be used to implement complex decision-making logic in Verilog code. It is a versatile tool that can be used in a variety of situations.

In this article, we have explored the "else if" statement in detail. We have discussed its purpose, syntax, and usage. We have also provided some tips for using the "else if" statement effectively.

We encourage you to experiment with the "else if" statement in your own Verilog code. By doing so, you will gain a better understanding of its power and versatility.

Unveiling Rachel Jane Conn's Age: A Journey Of Privacy And Personal Choice

Unveiling The Secrets Behind Hailey Rae Ostrom's Age: Discoveries And Insights

Discover The Secrets To Ellie Botterill's Net Worth